Технологии микроэлектроники на пальцах. «Закона Мура», маркетинговые ходы и почему нанометры нынче не те нанометры

12-04-2019, 14:46. Разместил: Редакция ОКО ПЛАНЕТЫ

Продолжение. Начало здесь - https://aftershock.news/?q=node/745507

Рассмотрели вкратце технологии микроэлектроники и технологические ограничения. Теперь поговорим о физических ограничениях. Физических эффектов. которые влияют на размеры элементов в транзисторе, много. Пройдемся по основным.Здесь придется уже влезть в физику, иначе никак.

Для начала порядок некоторых величин:

- Концентрация атомов кремния в кристалле – 1022/см3

- Концентрация собственных электронов и дырок при комнатной температуре – 1010/см3

- Концентрация примесных атомов с слаболегированных областях – 1016-1018/см3

- Концентрация примесных атомов с сильнолегированных областях – 1019-1020/см3

- Концентрация примесных атомов с очень сильнолегированных областях – 1021. В этом случае говорят уже о вырожденном полупроводнике, поскольку такая концентрация (один атом примеси на 10 и менее атомов кремния) меняет энергетическую структуру кристалла.

Зависимости характеристик кремния от температуры.

Туннельный ток.

Область пространственного заряда (ОПЗ).

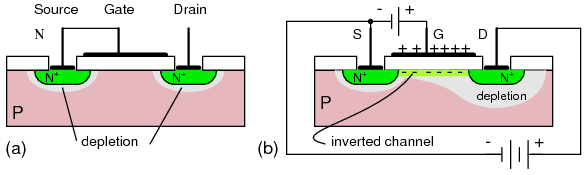

Если перевести эту модель на наш полевой транзистор то получаем картинку ниже:

Светло-розовым обозначены обедненные области (ОПЗ). Получаем что реальная ширина активной базы (которая управляется напряжением затвора) меньше расстояния исток-сток. Это размер базы минус ширина ОПЗ переходов. При отсутствии напряжения питания ширина ОПЗ истока и стока одинаковые. Если подать рабочее напряжение, ширина ОПЗ стока растет, поскольку она находится под обратным смещением. Активная база сужается еще больше.

Если база будет слишком короткой, то ОПЗ стока и истока соединяются. Ширина активной базы становится равна 0, от стока к истоку потечет сквозной ток, транзистор открывается. Независимо от напряжения на затворе. Транзистор становится неуправляемым. Эффект называется «прокол базы».

Есть еще промежуточный вариант, когда ОПЗ не смыкаются, но расстояние от истока до границы ОПЗ стока меньше 8 нм. Тогда в это ОПЗ начинают туннелировать электроны из истока. Попав в ОПЗ они электрическим полем перекидываются в сток. Проще говоря от истока к стоку потечет приличный туннельный ток.

Лавинный пробой.

Электрическое сопротивление областей.

А теперь рассмотрим действие этих эффектов в совокупности.

Главной угрозой при миниатюризации транзисторов является прокол базы. Чтобы его убрать, нужно уменьшить ширину ОПЗ. Уменьшить его можно снижая внешнее напряжение и увеличивая концентрацию примесей в базе.

Напряжение питания снижать уже некуда, оно и так в районе 1В – около двух пороговых. Если сделать еще меньше, то рискуем получить «невнятное» открытие транзисторов из-за электрического сопротивления.

Можно повысить концентрацию примесей в базе, но тогда получим:

- резкий рост туннельного тока утечки из стока в базу;

- повышение риска получить лавинный пробой перехода;

- увеличение порога напряжения для индуцирования канала, с риском получить пробой подзатворного диэлектрика.

Из-за этих ограничений концентрация примеси в базе фиксируется на уровне 1018-1019.

Все названные и неназванные факторы дают ограничение минимальной ширины базы для кремниевых МОП-транзисторов в районе 25 нм. Можно меньше, но ток утечки становится неадекватным и вероятность сбоя растет по экспоненте.

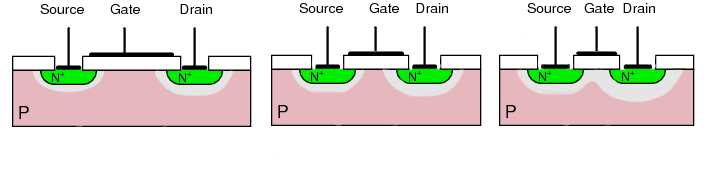

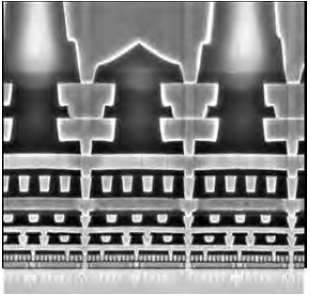

Картинка в подтверждение:

Фото транзисторов, выполненных по 90 нм и 32 нм технологиям. Снято в одном масштабе. Как видим размеры металлических контактов стали меньше в разы, а вот ширина базы практически не изменилась. Все те же 25 нм. Больше того, для транзисторов по технологии 14 нм, 10 нм и 7 нм она та же самая.

Впервые столкнулись с этим при переходе от 130 нм к первым сериям 90 нм. Тогда впервые не смогли уменьшить ширину базы пропорционально всем остальным размерам, она осталась примерно 35 нм. Позднее ее таки снизили до 25, но с тех пор ширина базы уже не подчинялась пропорциям технорм. И чем меньше становились транзисторы, тем сильнее это проявлялось.

Нужно было менять критерии норм техпроцессов. Что же сделали. Большинство ничего не сделали. Они продолжали выдавать за норму техпроцесса разрешение фотолитографии. Или минимальную ширину дорожки металлизации как проявление наиболее простой и наглядной операции.

Креативнее всего поступили маркетологи Intel. Они стали вычислять норму техпроцесса из размера элементов. Т.е. берется площадь шеститранзисторной ячейки статической памяти. В технологии с разрешением литографии 65 нм она была 0,77 мкм2, а при разрешении 40 нм она стала 0,37 мкм2. Если бы размеры транзисторов как раньше уменьшались пропорционально, то это соответствует технологии 45 нм. Значит будем считать что у нам 45 нм технология. Отсюда и пошли расхождения технорм от Intel с другими – 28 нм у всех, 32 нм у Intel; 20 нм у всех, 22 нм у Intel; 10 нм у всех, 14 нм у Intel.

Как показала дальнейшая история, Intel в итоге оказался честнее конкурентов.

Рассмотрим влияние токов утечки.

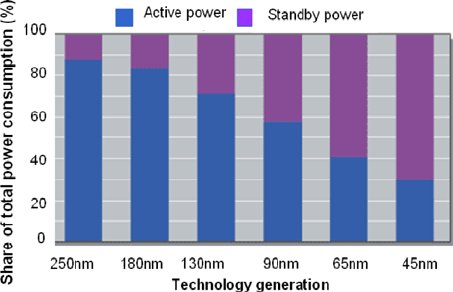

Есть замечательный график

Показывает процентное отношение рабочего и паразитного энергопотребления. Синий – энерговыделение как результат токов перезарядки (рабочий ток), фиолетовый – результат токов утечки (паразитный ток). Это с учетом мер, которые все это время предприняли для снижения паразитных токов.

Хорошо видна причина, по которой прекратился рост тактовых частот процессоров. Первые процессоры в 3 ГГц появились в начале 2000-х. Так на этом уровне и остались. Обычно это объясняют тем, что увеличилось число ядер, логика стала сложнее, углубилась конвейеризация, поэтому выросли требования к стабильности и вообще не в гигагерцах счастье. Частично верно. Но раньше как-то умудрялись сочетать все эти факторы с ростом частот.

Дело в том, что раньше при уменьшении размера транзисторов появлялся резерв по энергопотреблению. Например, технорма уменьшилась в 2 раза, число транзисторов выросло в 4 раза, а среднее энергопотребление каждого транзистора снижалось в 6-7 раз. Дело в том, что КМОП транзисторы потребляют ток при переключении, а рост числа транзисторов шел преимущественно за счет роста кэш-памяти. Транзисторы памяти переключаются относительно редко. Поэтому потребляли меньше, чем активные элементы процессора.

Эта разница и давала возможность поднимать тактовую частоту при том же тепловыделении

При переходе со 180 нм к 130 ток утечки съел эту дельту. С тех пор несмотря на все ухищрения в плюс так и не вышли. Все пожрал проклятый долгоносик съедают токи утечки. где-то даже ушли в минус, например для энергосберегающих процессоров пришлось снижать частоту. Если чудесным образом убрать утечки, для 45 нм технологии видим 3-кратный запас для роста частоты.

По сути в течении 2000-х годах тихим сапом произошла смена приоритетов. Раньше приоритетом было уменьшение размеров транзиторов. Сейчас в приоритете сокращение утечек.

О методах борьбы с утечками.

Смена материала подзатворного окисла.

С переходом на High-K диэлектрики пришлось менять и материал затвора. Вместо поликремния стали вновь использовать металл, обычно силицид никеля NiSi. Для разделения со вторым и далее слоем металлизации по прежнему используют окисел кремния.

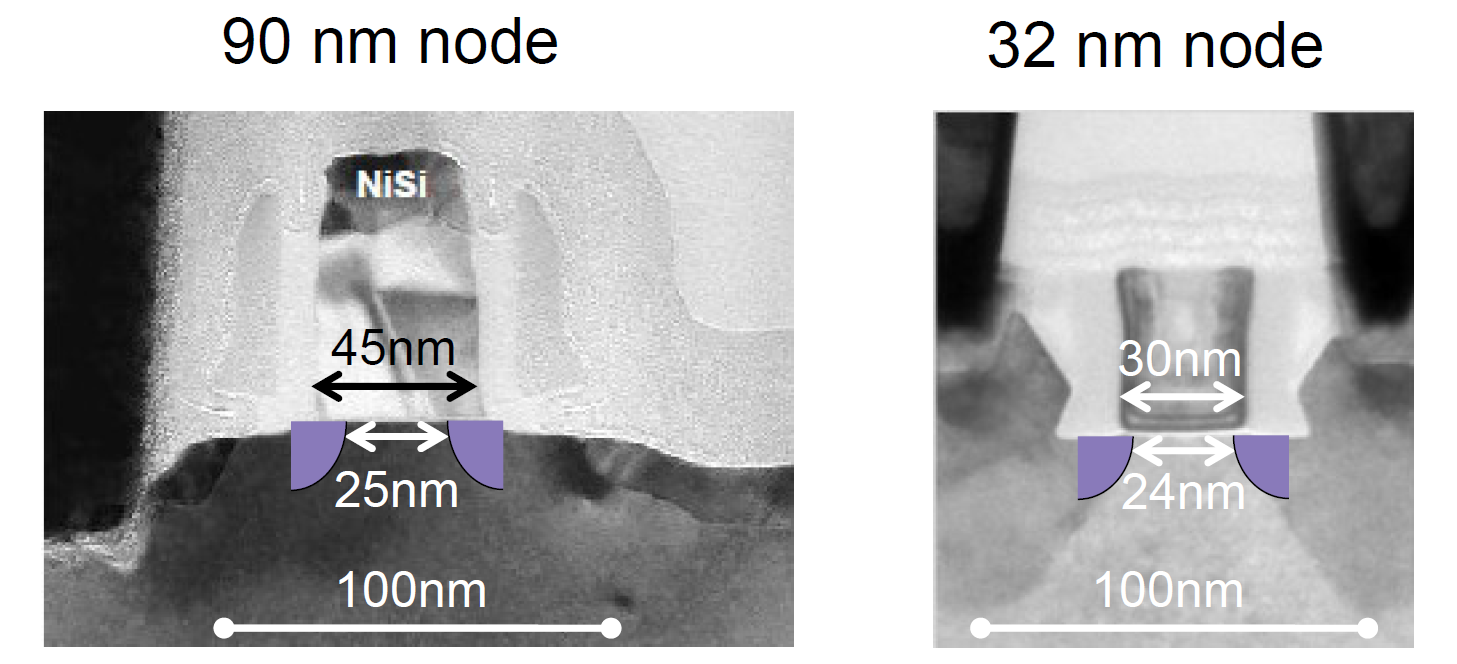

Кремний на изоляторе (SOI)

Технология кремний на изоляторе, он же КНИ, он же SOI использовался и раньше для изоляции ячеек. Здесь же пошли еще дальше. Поверх кремниевой подложки формируют слой окисла, а нем эпитаксиально наращивают слой кремния. На картинке схематически разница SOI-технологии с обычной планарной МОП.

![]()

Эта технология кардинально сокращает токи утечки.

Но есть и недостатки. Технология КНИ пока очень сложная и дорогая. Кроме того из-за тонкой изолированной базы проблемы с накоплением достаточного количества электронов или дырок для формирования канала. Канал получается очень узкий. Другой проблемой становится отвод тепла. Окисел кремния имеет низкую теплопроводность и отвод тепла с пленки в массу подложки затруднен. Как вариант вместо окисла кремния можно использовать сапфир Al2O3, у него теплопроводность выше. В идеале окисел должен был бы быть под стоком и истоком, но его не было бы под базой. Тогда в сочетании с High-K диэлектриком можно было бы нарастить концентрацию примесей в базе и уменьшить ширину канала до 15 нм.

Пока использование этой технологии ограниченное.

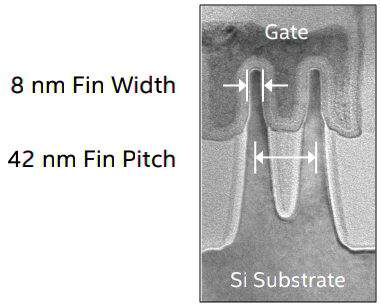

FinFET транзисторы.

Название от английского Fin – плавник. гребень. Технология впервые была использована на 22 нм технорме и на данный момент является доминирующей в производстве процессоров. Суть в том, что эпитаксиально наращивается не полный слой кремния поверх окисла, а отдельные гребни в очищенных от окисла зонах.

Вот схематическое сравнение с планарной технологией. Как видим транзисторы становятся трехмерными.

Затвор в данной технологии обтекает канал с трех сторон. Когда подаем напряжение на затвор, он вытягивает электроны (дырки) из глубины к вершинам гребней и в них формируется канал. Таким образом вся активная зона стока, истока и затвора уходит в гребни, утечка токов вглубь подложки минимальна. При этом термически гребень не изолирован от подложки и тепло свободно уходит вниз.

Обычно используют двух- или трехгребневые (трехзатворные) транзисторы. При таких размерах сделать прямоугольные гребни как на схеме нереально, по форме это скорее усеченный конус.

А вот вид сверху. То, что выпирает над окислом, верхушка нанометрового айсберга. Основания гребней намного шире и здесь не видны.

Справа снизу наш КМОП транзистор. Видим 6 гребней, 3 для n-канала, 3 для p-канала, в середине поперек затвор, по краям контакты к стоку и истоку. Размер транзистора определяется расстоянием между гребнями, числом гребней, шириной канала (все те же 25 нм и больше), размером областей стока и истока. Разрешение фотолитографии на размер транзистора влияет опосредовано через возможность сокращения шага между гребнями. Например в 22 нм технологии шаг между гребнями 54 нм, в 14 нм – 42 нм, в 10 нм – 34 нм. Как видим у тут линейной зависимости не наблюдается.

Сейчас в мире есть 3 компании, которые освоили эту технологию. Это американский Intel, корейский Samsung и тайваньская TSMC. Даже бывшая дочка AMD – GlobalFoundries – выбыла и з процесса. Сейчас AMD заказывает процессоры у TSMC и заключила договор с Samsung.

Немного о металлизации. Металлические дорожки в первом, самом нижнем слое металлизации всегда старались делать минимальными. Дело в том, что дорожка металлизации образует с кремнием все тот же плоский конденсатор металл-диэлектрик-кремний. Но в отличии от затвора это паразитный конденсатор. При большой емкости на частотах в гигагерцы может возникнуть паразитная электрическая связь там, где ее быть не должно. Чтобы уменьшить паразитную емкость нужно уменьшать площадь дорожек. Поэтому дорожки в первом первом слое металлизации делают максимально короткими и минимально тонкими. По этой же причине стараются чтобы разные слои металлизации перехлестывались под прямым углом – сначала делают продольные дорожки, следующим слоем поперечные дорожки. Чем выше находится слой, тем толще окисел под ним и шире дорожки.

К чему это я. Поскольку толщина первой металлической дорожки минимальная, то ее часто указывают в качестве нормы техпроцесса. В технологии FinFET пространство между гребнями заполняется окислом. Довольно толстым слоем поверх High-K диэлектрика, затвора, гребней и впадин Первый слой металлизации выводят на эти завалы над впадинами. Сами дорожки делаю шире для уменьшения электрического сопротивления и компенсации неровностей. Т.е. минимально возможная ширина дорожки и реальность тоже разошлись.

Т.е. норма техпроцесса все больше становится виртульной величиной. Поэтому мы имеем близкие по параметрам процессоры, маркируемые нормами от 7 нм до 22 нм. FinFET 22 нм процесс позволяет обходиться двумя гребнями, в 7 нм нужно 3 гребня, в результате размеры транзисторов примерно одинаковые. Тем не менее в журналах часто продолжают писать, что с переходом с 10 нм на 7 нм число транзисторов увеличится в 1,8 раза. У людей все еще работают старые шаблоны эпохи Мура.

Что же дальше. Переход к объемным транзисторам привел к появлению большого количества перспективных модификаций. Например Samsung анонсировал технологию GAAFET для технормы в 5 нм.

Т.е. гребень должен быть не сплошной, а разделен на отдельные нити. Вопрос стоит ли овчинка выделки. Есть варианты кольцевых затворов, вертикальных и пр. Есть сочетания FinFET и SOI. Вообще химические процессы эпитакции сложнее, но более линейны и предсказуемы, чем литография. Это обеспечивает большую точность и возможность создавать более тонкие объемные структуры.

Ситуация на современном рынке производителей микропроцессоров и перспективы.

Итак выделилась тройка лидеров - Intel, Samsung и TSMC. Intel проводит под собственными брендами, остальные преимущественно на заказ. Под брендами AMD, NVIDIA, Qualcomm, Apple, IBM скрываются микросхемы, произведенные на заводах TSMC или Samsung. Некоторые старые лидеры отвалились или уперлись в преграду. В высшую лигу пытаются прорваться китайцы, но пока не очень успешно. Не хватает собственной технологической базы, а мировые лидеры в производстве оборудования новейшие технологические линии для китайцев придерживают.

Оптимизм экспертов связан в переходом на обхемные структуры и начало использования EUV-литографии. Samsung и TSMC начали ограниченно ее использовать, для наиболее тонких структур. Это дает им возможность рапортовать о достижении норм в 7 нм и в перспективе до 5 нм. Хотя, как уже описал, эти цифры на самом деле на мало что влияют. Тот же Intel вообще отказался от EUV. Видимо не верят что это сильно улучшит характеристики.

С другой стороны, люди в теме понимают что эпоха Мура закончилась, и каждый новый шаг роста производительности потребует все больших усилий и времени. Бурный рост микроэлектроники заканчивается. Как это случилось когда-то в автомобилестроении и авиации. После взрывного роста следует медленное развитие.

Из перспективных точек прорыва можно выделить переход на другой материал (не кремний) и создание многослойных микросхем (3D-интеграция). Для 3D интеграции придется кардинально снизить тепловыделение или усилить теплоотвод.

Это все что касается размеров транзисторов. Большие резервы роста производительности есть в другом. В оптимизации архитектуры например. Можно даже сделать маркетинговый ход, мол новый процессор с улучшенной архитектурой работает как если бы это был старый с технологией 0,5 нм. Поэтому маркируем его как 0,5 нм. И фиг с ним что размеры транзисторов те же самые.

Возможно создание новых типов ячеек из комбинаций транзисторов. Например, вместо 6 транзисторной ячейки памяти сделать 2 транзисторные структуры со сложной физикой взаимовлияния. Объемные структуры здесь дают множество возможностей.

Предельные физические ограничения.

Кто-то может сказать, что мой пессимизм необоснован. Находят же способы обойти ограничения. Может не так быстро как раньше, но тем не менее.

Дело в том, что есть еще физические процессы, которые обойти никак не получится. Основые их них – вещество состоит из атомов, а носителями заряда являются электроны. Создать транзистор меньше атома никак не получится. Его не получится создать даже меньше 1000 атомов. Потому что есть электрон и соотношение неопределенностей Гейзенберга. Электрон очень непостоянная частица, более-менее стабильное поведение возможно только для массива из тысяч и миллионов электронов. На одном электроне можно только загубить кота Шредингера.

Даже при нынешних размерах случаются коллизии из-за самопроизвольного срабатывания транзисторов. Если вероятность коллизии 1 / 109, при числе элементов в миллиарды и частотах в ГГцы это дает в среднем 1 коллизию за цикл, или несколько миллиардов коллизий в секунду. Для их отлавливания есть системы контроля целостности операций, подозрительная операция отправляется на повторное выполнение.

По мере миниатюризации число коллизий начинает очень резко расти. В результате приходим к ситуации нулевого или даже отрицательного эффекта от миниатюризации. Т.е. транзисторы сделали меньше, их влезает в кристалл больше. Но из-за роста коллизий и циклов повторной обработки, суммарная производительность не выросла. А может даже упала. И этот порог вполне на горизонте.

Несколько слов об отечественной цифровой микроэлектронике.

Вопреки расхожим мнениям, до 1985 года отставание СССР от лидеров было не таким уж и большим. Примерно 3-4 года. Это если брать предприятия-лидеры в Зеленограде. В условиях действия работы закона Мура даже отставание в 3-4 года сильно влияло на характеристики. Проблемы были с получением качественного окисла, с четкостью p-n-переходов. Если к этому добавить консервативную политику с упаковкой чипов в корпус, а также советские нормативы производства плат и корпусов с кучей железа (кто разбирал советские магнитофоны, тот поймет), получаем анекдот про советскую микросхему с чугунными ручками для переноски.

Причин отставания много. Позднее стартанули, ограниченные ресурсы, распыление ресурсов. Когда американцы сосредоточились на КМОП, наши продолжали экспериментировать с различными технологиями. Довольно активно работали с альтернативами кремния, прежде всего с материалами A3B5. Ну и общая расслабленность позднесоветских НИИ.

После 1985-го американцы резко стартанули, а у нас начались проблемы. Далее 1990-е, когда жизнь в отрасли теплилась по инерции. В итоге в 21 век вошли с технологией 800 нм, когда лидеры уже штурмовали 130 нм. Вторую жизнь отрасли дала массовая чипизация карт и госзаказ. Главным производством стали чипы для SIM-карт, банковских карт, карт оплат, транспортных и скидочных карт и пр. Там не нужны большие гигагерцы и маленькие нанометры.

Тем не менее идет попытка выйти и в «высшую электронику». Развитие идет по четырем основным направлениям.

1. «Суверенные» техпроцессы. Это попытка создать полный цикл производства на аппаратуре отечественного производства и собственными техпроцессами. Идем тем же путем, который прошли лидеры лет 20 назад, но с учетом найденных граблей и путей решения. Из последнего что было в открытых источниках это 250 нм в серии и 150 нм в процессе внедрения. Сюда же можно отнести попытку создать собственные установки EUV-литографии на 13,5 нм и таким образом сразу выйти если не в высшую лигу, то вплотную к ним.

2. Закупка технологических линий у ведущих мировых производителей. Проблема тут в том, что самые современные установки нам не продавали даже в лучшие годы. Обычно продают устаревшие линии, которые сняли с производства. Сейчас в связи с санкциями тем более. Тут можно вспомнить эпопею с закупкой «Ангстремом» оборудования дрезденского завода AMD в 2007, под техпроцесс 180 нм. Или закупку «Микроном» 90 нм линии у французской STMicroelectronics с последующим апгрейдом до 65 нм. Пока это самый тонкий техпроцесс в России, успели урвать перед санкциями. Правда есть сейчас и обходной путь – закупка через Китай.

3. Заказ производства на заводах в Китае или Тайване. При этом архитектура и топология полностью разрабатываются у нас, сейчас даже делаются собственные фотошаблоны. Китайцам остается только воспроизвести техпроцессы на своих заводах. Получаем более совершенные производительные процессоры, и развиваем компетенцию в области разработки самых современных процессорных систем. Здесь задействованы уже не группа ученых-кулибиных, а большие конструкторские коллективы. Из полного цикла выбывает только последний участок – производство.

4. Развитие альтернативных технологий. Это разработка перспективных технологий, которые могут стать массовыми в будущем. Сюда входят работы по соединениям A3B5 и гетероструктурам, прежде всего арсениду и нитриду галлия. А также попытки оптимизировать электронно-лучевую и рентгеновкую литографию для массового производства, что вообще снимает ограничения литографии.

В целом для российской микроэлектроники ситуация не блестящая. Но есть надежда что лидеры неизбежно затормозятся из-за физических ограничений, и тут мы медленно поспешая подкрадемся сзади.

Вернуться назад